# DIE EUROPÄISCHE REFERENZ FAB

# BLAUPAUSE FÜR VERTRAUENSWÜRDIGE UND SKALIERBARE HALBLEITERFERTIGUNG IN EUROPA

#### Exposé:

Die gläserne Referenz-Fab ist ein modularer 300-mm-Blueprint (130→65 nm, Packaging-First) mit offenen PDKs, auditierbaren Prozessen und Comply-to-Connect-Label. Sie skaliert als Netzwerk klonbarer Fabs, monetarisiert über Trusted-Premium und Advanced-Packaging-Leistungen und bleibt dabei freiwillig sowie EU-rechtskonform kooperativ. Tranchierte Finanzierung koppelt Auszahlungen an Meilensteine (Bau/Tool-IQ-OQ, PDK/MPW, Audit-Go-Live, 65-nm-Release); Governance-Optionen (PPP, SPV, Stiftung; privat mit Public-Service-Mandat) bleiben offen. Phase 0 validiert Standort, CAPEX/OPEX-Korridore, Nachfrageanker (LTAs/Take-or-Pay) und die RefFab-Academy. Empfehlung: EU-Task-Force in 6–12 Monaten zur Pilotierung; parallel Industrie-MoUs für MPW und Packaging-Pilot. Alle Kennzahlen als Korridore; Validierung in Phase 0.

Packaging-First. Trusted by Design.

# Gläserne Muster-Fab für Europa: Offene, skalierbare Halbleiterfertigung als Strategiekonzept

## **Executive Summary**

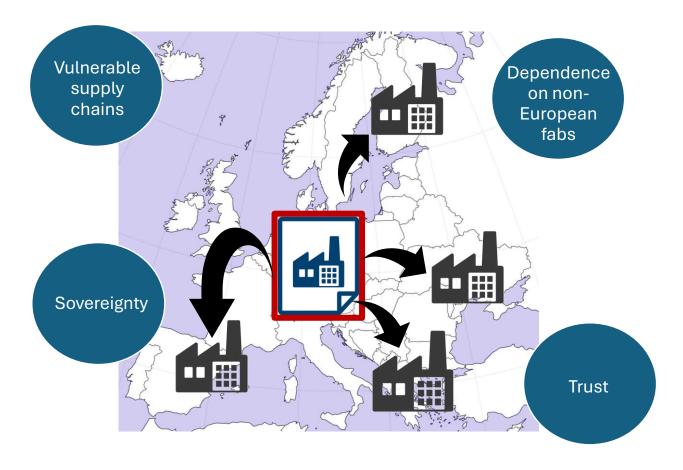

Europa steht 2025 vor der existenziellen Aufgabe, seine technologische Souveränität in der Halbleiterproduktion zu stärken. Der European Chips Act von 2022 setzte sich zum Ziel, den europäischen Anteil an der weltweiten Chipfertigung bis 2030 von unter 10 % auf 20 % zu erhöhen – ein ambitioniertes Vorhaben, das Investitionen von insgesamt rund 43 Mrd. € mobilisieren sollte<sup>1</sup>. Inzwischen fordern jedoch alle 27 EU-Staaten im Rahmen einer Semicon Coalition eine Weiterentwicklung zum "Chips Act 2.0". Dieses zielt weniger auf reine Marktanteile ab, sondern auf das Schließen kritischer Lücken: Schlüsseltechnologien sollen gesichert, Genehmigungsprozesse beschleunigt und Kompetenzen entlang der gesamten Wertschöpfungskette in der Mikroelektronik vertieft werden<sup>2</sup>. Parallel warnt die EU-Agentur für Cybersicherheit (ENISA) vor zunehmenden Cyberangriffen auf kritische Infrastrukturen – ein Weckruf, dass vertrauenswürdige, auditierbare Hardware zur Sicherheitsfrage geworden ist. Weltweit treiben andere Industrienationen den Halbleiterausbau voran: Japan investiert Milliarden in die Rapidus-Initiative (Ziel: 2-nm-Massenfertigung bis 2027)3, und die USA haben mit dem CHIPS and Science Act ein 52-Mrd.-\$-Programm gestartet, gefolgt von Großinvestitionen wie Texas Instruments' über 60 Mrd. \$-Vorhaben für neue Fabs in Texas und Utah<sup>4,5</sup>. Auch China flutet die Branche seit Jahren mit Fördergeldern, um eigene Fabs hochzuziehen. Im europäischen Raum gibt es zwar vereinzelte Initiativen – etwa Irlands "Silicon Island"-Strategie (Nationale Halbleiteroffensive seit 2025)<sup>6</sup>, das von der ETH Zürich mitgetragene Schweizer "Chip FabLab"-Projekt<sup>7</sup> oder Pläne um das CSIC/CNM in Spanien. Diese Einzelbemühungen sind

<sup>&</sup>lt;sup>1</sup> https://commission.europa.eu/strategy-and-policy/priorities-2019-2024/europe-fit-digital-age/european-chips-act\_en

<sup>&</sup>lt;sup>2</sup> https://digital-strategy.ec.europa.eu/en/news/semicon-coalition-calls-reinforced-chips-act

<sup>3</sup> https://www.rapidus.inc/en/tech/te0006

<sup>&</sup>lt;sup>4</sup> https://bidenwhitehouse.archives.gov/briefing-room/statements-releases/2022/08/09/fact-sheet-chips-and-science-act-will-lower-costs-create-jobs-strengthen-supply-chains-and-counter-china

<sup>&</sup>lt;sup>5</sup> https://www.ti.com/about-ti/newsroom/news-releases/2025/texas-instruments-plans-to-invest-more-than--60-billion-to-manufacture-billions-of-foundational-semiconductors-in-the-us.html

<sup>&</sup>lt;sup>6</sup> https://enterprise.gov.ie/en/publications/silicon-island-a-national-semiconductor-strategy.html

<sup>&</sup>lt;sup>7</sup> https://ee.ethz.ch/news-and-events/d-itet-news-channel/2025/08/boosting-swiss-semiconductors-plans-for-chip-factory-gain-media-attention.html

wichtig, können aber mangels kritischer Masse das Grundproblem nicht lösen. Europa muss seine Strategie bündeln und als Einheit handeln, um gegen geopolitische Risiken, Lieferengpässe und Technologierückstand gewappnet zu sein. Vor diesem Hintergrund präsentiert dieses Papier das Konzept einer gläsernen Muster-Fab als proaktive Antwort.

Die **gläserne Muster-Fab für Europa** ist ein vorgeschlagenes Referenz-Halbleiterwerk, das **offen, skalierbar und serienreif** gestaltet ist. Sie dient als Open-Source-Blaupause für den schnellen Aufbau weiterer Fabs in Europa. Kernprinzipien dieses Ansatzes sind:

- Serienfähiges Fertigungsmodell statt Pilotlinie: Anders als übliche Pilotlinien (die oft nur Demonstrationscharakter und im besten Fall Kapazitäten für Kleinserienfertigung haben) wird die Muster-Fab von Anfang an auf industrielle Stückzahlen und 24/7-Betrieb ausgelegt. Sie soll reale Produktionslasten stemmen und wirtschaftlich arbeiten, damit jedes nach diesem Vorbild kopierte Werk sofort produktionsreif ist und keine aufwendige Umstellung von Pilot- auf Serienbetrieb nötig wird.

- Transparente Open-Source-Blaupause: Alle wichtigen Prozesse, Anlagenparameter und Betriebsabläufe der Fab werden prinzipiell offen und für die Wiederverwendbarkeit dokumentiert und zugänglich gemacht. Diese Transparenz erlaubt es europäischen Industrieakteuren und Staaten, die Fab als Bauplan zu nutzen, um eigenständig neue Werke mit geringerem Entwicklungsrisiko aufzubauen. Zum anderen schafft eine solche offene Architektur Vertrauen in die gefertigten Chips: Sicherheitsrelevante Halbleiter können bis hinunter auf Prozessebene geprüft werden, was vertrauenswürdige Elektronik "Made in Europe" sicherstellt. Etwaige Hintertüren oder Manipulationen lassen sich in einem gläsernen Fertigungsprozess erheblich schwerer verbergen. Open-PDK & Open-Source-EDA: Auf Basis offener PDKs und reproduzierbarer, auditierbarer Toolflows (CI/CD) werden Referenz-IPs und Assembly-Design-Kits bereitgestellt; so sinken Eintrittshürden und Auditzeiten messbar. So strebt das Projekt das Gütesiegel "Trusted EU Fab Network" an unabhängige Stellen sollen anhand der offenen Unterlagen und Inspektionen die Vertrauenswürdigkeit der Produktion zertifizieren.

- Packaging-First & Chiplet-Readiness: Leistungs-, Energie-, Zuverlässigkeits- und Sicherheitsziele werden heute im Back-End/SiP/SoP entschieden. Deshalb ist Advanced Packaging ab Tag 1 Kernbestandteil: RDL/Fan-Out, Interposer/2.5D und Co-Packaging von Leading-Edge-Compute-Dies mit 65-nm-Peripherie (PMIC, Mixed-Signal, Sensor-IF). Wir verankern Chiplet-Standards (z. B. UCIe/BoW/OpenHBI), Design-for-Packaging und qualifizierte Test-Flows (KGD→SLT). So vergrößern wir den Abstand zur Leading Edge nicht, sondern überbrücken ihn systemisch. Hier muss es einen engen Austausch mit EU-geförderten Pilotlinien (z. B. APECS) geben.

- Fokus auf 65-nm-CMOS als strategischer Technologieknoten: Die Muster-Fab zielt auf den etablierten 65-nm-Knoten ab, da dieser für viele kritische Anwendungen zukunftsfähig und ausreichend performant ist. Sektoren wie Automobil, Industrie, Medizintechnik und Luft-/Raumfahrt können ihre Mikrocontroller, ASICs und Mixed-

Signal-Bausteine mit 65 nm Strukturbreite fertigen – robust, kosteneffizient und in hohen Stückzahlen. Prognosen zeigen, dass auch nach 2030 noch ein erheblicher Anteil der globalen Chipnachfrage auf Technologien ≥65 nm entfallen (v.a. analoge/leistungselektronische Chips), während <10 nm nur ~12 % ausmachen. Als Brückentechnologie wird anfänglich mit dem bewährten 130-nm-Knoten gestartet, für den sofort Equipment und offene Prozessdaten und PDKs in Europa vorhanden sind. Diese Brückentechnologie erlaubt einen schnellen Produktionsbeginn mit hoher Ausbeute, während parallel die 65-nm-Linie hochgefahren und zur Reife gebracht wird. Die Fab-Infrastruktur wird modular so konzipiert, dass ein späteres Upgrade auf 65 nm (oder kleiner) ohne Grundneuplanung möglich ist. Der Fokus bleibt jedoch zunächst auf 65 nm als "Sweet Spot" zwischen Reife, Verfügbarkeit und Souveränitätsgewinn. Wichtig: Für ausgewählte Plattformen wird eine **Langzeitverfügbarkeit** (Zielkorridor ≥ 15 Jahre) mit Obsoleszenz-Pfade zugesichert; Zertifizierungs- und Qualifikationspfade (z. B. AEC-Q100/IEC 61508/DO-254) sind Teil des Angebots. Damit wird bewusst kein Commodity-Volumenmodell verfolgt, sondern ein Trusted-Premium-Ansatz mit Service- und Qualitätsprämien.

- Datengetriebene Fertigung, Audit-Trails & Automatisierung: Dichte Inline-Metrologie, SPC/ML-gestützte Regelung und durchgängige Rückkopplung von Front-/Back-End-Daten verkürzen Ramp-Ups und schaffen prüfbare Qualitäts- und Vertrauensmetriken, hierzu gehören auch robotikbasierte Automatisierungsprozesse. Dort, wo es sinnvoll ist, kommen selektive Single-Wafer-Schritte zum Einsatz; Ofen-/Batch-Prozesse bleiben wirtschaftlich.

- Nutzung bestehender Ressourcen und Expertise: Die Muster-Fab soll räumlich eng an bestehende Forschungs- und Pilotlinien wie IHP, CEA-Leti oder imec angebunden werden, um vorhandenes Prozess-Know-how unmittelbar in die industrielle Umsetzung zu überführen. Diese Nähe ermöglicht einen signifikant beschleunigten Ramp-up, da etablierte Teams, qualifizierte Anlagen und bewährte Prozessmodule direkt genutzt werden können.

Gleichzeitig bleibt die Muster-Fab institutionell eigenständig sie ist keine Erweiterung einer Forschungseinrichtung, sondern eine industrielle Referenz-Fab mit eigenem Mandat. Durch die gezielte Integration von Forschungs-Know-how in ein offenes Produktionsmodell kann Europa schneller handlungsfähig werden, ohne bei Null zu starten.

- Governance & Public-Trust-Mandat (PPP): Öffentliche Eigentümerschaft bzw.

Public-Trust-Mandat institutionell unabhängig von F&E-Einrichtungen, bei räumlicher Nähe/Ko-Lage; Nicht-Diskriminierung, offene Audit-Schnittstellen (Traceability bis Los-/Wafer-Ebene), klare Zugangsregeln; Co-Invests der Industrie in Equipment/Packaging. Das sichert Replizierbarkeit, Planbarkeit und überprüfbare Vertrauensmechanismen.

- Talent, Ausbildung & Trusted Personnel (RefFab Academy): Die Muster-Fab verankert Qualifizierung als Kernaufgabe. Die RefFab Academy liefert zentrale Curricula, EQFfähige Micro-Credentials und einen Skills-Passport, der direkt mit RBAC/Comply-to-Connect im MES verknüpft ist. Packaging-First (SiP/UCle, RDL/Fan-Out, ATE/SLT) startet ab Tag 1; Ausbildung erfolgt in standardisierten Learning Cells und einer "Lernwerkstatt-in-a-Box" (on-/off-the-job, Bootcamps, VR/AR, Digital-Twin). Duale/VETund Hochschulpfade werden über MoUs an bestehende Programme angedockt; Rotationen (Fab/OSAT/F&E) verkürzen die Time-to-Competence. Aktives Recruiting (EU-Programme, Umschulungen, internationale Anwerbung) wird flankiert durch familyready Angebote (schichtkompatible Kinderbetreuung, Sprachtracks, Mentoring; Just-Culture). GDPR-konforme, risikobasierte Background-Checks und ein Compliance-Gate (Antitrust/FDI/Dual-Use/IP/Privacy) sichern Veröffentlichungen und Artefakte. Offene PDKs/EDA & frei verfügbare ADKs sowie MPWs bleiben Lehrfundament. Zielkorridor pro Referenz-Fab in der Aufbauphase: 30–50 Ingenieur:innen und 70–120 Techniker:innen/Operator:innen p. a.; langfristig ca. 20 bzw. 60 p. a. (standortspezifisch in Phase 0 zu validieren).

- Skalierbare Musterlösung & Netzwerkgedanke: Übergeordnetes Ziel ist ein multiplikativer Effekt: Die Muster-Fab dient als Blaupause, die eins-zu-eins kopiert und in mehreren europäischen Regionen ausgerollt werden kann. Jede neue Fab nach diesem Modell erhöht sofort die regionale Fertigungskapazität und die Resilienz der Lieferkette. Durch Standardisierung der Architektur lassen sich sogar Fertigungslose und Personal zwischen Standorten austauschen. Fällt in einer Krisensituation eine Fab aus, können andere mit identischer Ausstattung temporär einspringen was die Versorgungssicherheit erhöht. Ein solches Netzwerk identischer, vertrauenswürdiger Fabs würde Europas Abhängigkeit von außereuropäischen Zulieferern reduzieren und gleichzeitig als Innovationsplattform dienen (z. B. gemeinsame Weiterentwicklung neuer Prozessmodule, offene IP-Bibliotheken).

- Spezialisierung für Nischenprodukte: Mehrere Fabs mit identischer CMOS-Basis können sich durch prozessmodulare Add-ons (z. B. HF-, Leistungs-, Sensor-Module, Photonik) zielgerichtet differenzieren ohne die Basistechnologie zu verändern. So verbinden wir Skaleneffekte mit technologischer Differenzierung in margenstarken Nischen. Damit entsteht ein flexibles Fertigungsökosystem, das Innovation und Spezialisierung im Nischenmarkt gleichermaßen fördert.

- Nachfrage-Anker: Öffentliche Beschaffung (KRITIS/Verwaltung/Sicherheit) sichert Grundlast; Industrie-Co-Invests heben Packaging-/Test-Kapazitäten. Abgrenzung: Keine EUV/Leading-Edge-Foundry, kein Commodity-Volumenmodell – Fokus auf Trusted-Premium, SiP/Chiplets und lange Produktlebenszyklen.

- Finanzierung & Wirtschaftlichkeit (Kurzüberblick): PPP-Struktur mit öffentlicher

Grundlast und Industrie-Co-Invests; Förderanteil an CAPEX (Standort/EU-Programme); stufenweises Funding nach Meilensteinen (MPW-Start, 65-nm-Ramp,

Packaging-Pilot); **Einnahmemix**: Foundry, Packaging/Test, Services (MPW, Zertifizierung, Obsoleszenz-Management).

Leitplanken (ohne starre Versprechen): MPW ≥ 4/Jahr (130 nm) & ≥ 2/Jahr (65 nm), SiP-MPW ab Jahr 2; Packaging-Ziele: RDL-Pitch 10 → ≤ 5 µm, Microbump ≤ 55 µm; Langzeit-Supply ≥ 15 J.; Trust-KPIs: veröffentlichte Yield-/DPPM- & Traceability-Kennzahlen.

Perspektive 2040+: Die Relevanz von ≥ 65-nm-Klassen bleibt aufgrund von Analog/Mixed-Signal-Anteilen, Leistungselektronik, eNVM-MCUs, HF/RF-Frontends, Rad-Hard-/Space-Elektronik und Sicherheitsanforderungen weit über die 2030er hinaus bestehen. Long-Lifecycle-Industrien (Automotive/Automation/MedTech/Aerospace) und Chiplet-Architekturen stabilisieren die Nachfrage zusätzlich: 65 nm übernimmt Peripherie, Sensorik, PMIC, Safety-MCU, während Leading-Edge-Compute via Co-Pack integriert wird. Das Netzwerk kann – wo sinnvoll – modular shrinken oder seinen SiP/OSAT-Footprint ausbauen, ohne das Geschäftsmodell zu verändern.

Diese Executive Summary richtet sich an politische Entscheidungsträger auf EU- und nationaler Ebene sowie an mögliche Fördergeber in Verwaltung und Industrie. Sie umreißt die Vision einer gläsernen Muster-Fab und deren Vorteile in kompakter Form. Die Empfehlung lautet, dieses strategische Konzept mit politischem Rückhalt und initialer Förderung zügig voranzutreiben. Angesichts der Reformbestrebungen im Chips Act, der verschärften Bedrohungslage und der weltweiten Investitionsdynamik ist **jetzt der richtige Zeitpunkt**, um die Grundlagen für eine offene und souveräne Halbleiterfertigung in Europa zu legen.

**Hinweis (Disclaimer):** Dieses Papier stellt ein Konzept vor und skizziert erste Vorschläge für Umsetzung und Finanzierung. Eine belastbare Realisierung erfordert jedoch eine vertiefte Analyse und einen detaillierten Ausführungsplan. Deren Erarbeitung ist integraler Bestandteil des Konzepts und Gegenstand der **Phase 0**.

# Annahmen, Geltungsbereich & Nichtziele

- Blaupause, keine Standort-/Finanzierungsentscheidung: Dieses Papier beschreibt eine replizierbare Reference-Fab-Blaupause (Fähigkeiten, Governance, Ausbildung) keine Standortwahl und kein Investitionsbeschluss.

- Kernfokus: Packaging-First (SiP/RDL/Fan-Out), Test/ATE/SLT, Open-PDK/EDA-Integration, Auditierbarkeit und Workforce-/Ausbildungspipelines.

- Technologiepfad: 130 → 65 nm als Evergreen-Knoten für AMS/MCU/PMIC/RF/IoT; konkrete Volumina/Produktmixe sind partnerspezifisch.

- Komplementärer Ansatz: Komplementär zu Leading-Edge-Fabs; Ziel sind Resilienz,

Qualifikation und KMU-Zugang nicht Volumenwettbewerb.

- **Phasenbasierte Umsetzung:** Phase 0 → Go/No-Go, mit messbaren Meilensteinen.

- Indikative Angaben: Quantitative Korridore sind szenariobasiert; alle Zahlen sind indikativ

#### **About the Authors:**

Norbert Herfurth earned his PhD (TU Berlin, 2020) in semiconductor failure analysis. 2013–2019 he worked in TU Berlin's Semiconductor Devices group. Since 2020 at IHP—initially as cross-department postdoc/project coordinator, now research group lead. He initiated and still shapes IHP's open-source activities (especially open source hardware and chiplet integration), including Europe's first open-source PDK.

Current employment is for identification only; views are personal.

Contact: ref-fab@hep-alliance.org

Arnd Weber is an economist and sociologist. Until retirement he was researcher at KIT, advising the EU Commission, EU Parliament and German government. His PhD traced the rise of public-key cryptography; he co-designed untraceable, loss-tolerant e-money, analysed the Dresden semiconductor cluster, and in 2003 predicted issues in European mobile data services. He founded "Quattro S" and helped initiate the HEP project on an open hardware security module. Currently he is subcontractor to IHP for the SIGN-HEP project (information is for identification only; views are personal). Contact: arnd.weber@alumni.kit.edu

Steffen Reith is Professor of Theoretical Computer Science at RheinMain University of Applied Sciences in Wiesbaden. During his work at Elektrobit Automotive, he developed products with cryptographic functions for use in current automobiles.

Contact: Steffen.Reith@hs-rm.de

Anna Herfurth is Head of Human Resources at IHP. She brings over six years of leadership experience in strategic HR, organizational development, and digital transformation. At IHP, she drives talent development, employer branding, and workforce structures for a high-tech research environment. In the Reference Fab initiative, she contributes expertise in HR strategy, skills pipelines, and dual education models for the semiconductor industry.

Current employment is for identification only; views are personal.

René Scholz earned a PhD in physics (MLU Halle-Wittenberg, 1999) after research on point-defect diffusion in Si and GaAs at the Max Planck Institute of Microstructure Physics. He joined IHP in 2001 for RF characterization and modeling, later leading the MPW Service and PDK development. He also holds an MBA (European University Viadrina, 2008). Recently, he contributes to IHP's open-source BiCMOS PDK.

Current employment is for identification only; views are personal.

www.linkedin.com/in/rene-scholz-86b4473

Torsten Grawunder is a hardware/security engineer. He studied physics of electronic components at TU Chemnitz, specializing in ASIC design for communication technology. Since 2021 he has worked at Swissbit Germany AG in system design/embedded solutions (APATS), creating and analyzing pre-development system concepts for future NAND-flash products and coordinating Swissbit's funding processes. Previously, for 20+ years, he developed encryption hardware for ISDN, ATM and Ethernet at Biodata, secunet and Rohde & Schwarz SIT.

Contact: torsten.grawunder@swissbit.com

### Liste der Abkürzungen (Executive Summary)

#### **Abkürzung Bedeutung**

ADK Assembly Design Kit

AMS Analogue and Mixed-Signal

ATE Automated Test Equipment

**CAPEX** Capital Expenditure

**CD/CI** Continuous Deployment / Continuous Integration

**ENISA** European Union Agency for Cybersecurity

**EQF** European Qualifications Framework

**FDI** Foreign Direct Investment

IP Intellectual Property

IQ/OQ Installation Qualification / Operational Qualification

**KRITIS** Critical Infrastructure (German: *Kritische Infrastrukturen*)

**LTAs** Long-Term Agreements

MES Manufacturing Execution System

ML Machine Learning

**MoU** Memorandum of Understanding

MPW Multi-Project Wafer

**OPEX** Operational Expenditure

**OSAT** Outsourced Semiconductor Assembly and Test

PDK Process Design Kit

**PMIC** Power Management Integrated Circuit

PPP Public-Private Partnership

RBAC Role-Based Access Control

RDL Redistribution Layer

SiP System-in-Package

SLT System-Level Test

SoC System-on-Chip

**SoP** System-on-Package

SPC Statistical Process ControlSPV Special Purpose VehicleTRF Transparent Reference Fab

**UCle** Universal Chiplet Interconnect Express

**VET** Vocational Education and Training

**WSPM** Wafer Starts per Month

## Weiterführende Informationen

**Landing Page & Downloads:** www.hep-alliance.org/Reference-Fab (QR-Code führt auf diese Seite)

**Kontakt & Briefing-Anfragen:** ref-fab@hep-alliance.org (oder: nor.herfurth@gmail.com)

#### Vorgeschlagene Zitation:

Herfurth, N., Weber, A., Reith, S., Herfurth, A., Scholz, R., & Grawunder, T. (2025). *The European Reference Fab – Blueprint for a Trusted and Transparent Manufacturing Network* (v2025-11-07). HEP Alliance. Verfügbar unter: hep-alliance.org/Reference-Fab

**Version & Updates:** v2025-11-07 · Diese Executive Summary ist ein "living document". Aktualisierte Fassungen werden auf der Landing Page veröffentlicht.