# THE EUROPEAN REFERENCE FAB

Blueprint For A Trustworthy And Transparent Manufacturing Network

Exposé:

The Transparent Reference Fab (TRF) is a modular 300-mm semiconductor fab blueprint designed as public-interest infrastructure to strengthen Europe's security, resilience and technological sovereignty. It combines a 130-nm industrial baseline with an optional evolution to 65 nm and a fully integrated packaging / Chiplet integration flow with open PDKs/ADKs and auditable processes from design via manufacturing to test. This enables the fully auditable production of extremely security-critical chips in Europe. The model scales as a network of clonable fabs. The TRF monetises via trusted-premium manufacturing and advanced-packaging services, and keeps all co-operation voluntary and EU-law compliant. Tranche-based financing links disbursements to milestones (construction and tool qualification, 130-nm PDK/MPW, audit go-live and – where pursued – 65-nm release); governance options (e.g. PPP, SPV, foundation; private with a public-service mandate) remain open. A planned phase 0 validates site options, CAPEX/OPEX corridors and a realistic capacity range, demand anchors (e.g. long-term agreements with public and industrial users), and the RefFab Academy.

Recommendation: set up an EU-level task force to steer Phase 0 and, in parallel, negotiate concrete agreements with industry for MPWs and a packaging pilot.

*From design via manufacturing to test.

Trustworthy by Design..*

Norbert Herfurth; Arnd Weber; Steffen Reith; Anna Herfurth; Rene Scholz;

Torsten Grawunder

ref-fab@hep-alliance.org

# Content

|                                                                                                   |    |

|---------------------------------------------------------------------------------------------------|----|

| Executive Summary .....                                                                           | 1  |

| Starting point: sovereignty under new conditions .....                                            | 9  |

| Objectives of the concept .....                                                                   | 11 |

| Technological roadmap: from pilot to network fab .....                                            | 13 |

| Phase 0 – Feasibility studies and consortium formation (9–15 months) .....                        | 13 |

| Phase 1 – Construction of the Reference Fab and parallel process development (30–36 months) ..... | 13 |

| Phase 2 – Commissioning of the Reference Fab (9–12 months) .....                                  | 14 |

| Phase 3 – Technological shrink to 65 nm / 55 nm (24–30 months) .....                              | 14 |

| Phase 4 – Networking, scaling, and consolidation (from Year 7–11) .....                           | 14 |

| Workforce and training strategy .....                                                             | 16 |

| Workforce pyramid and FTE corridors (base module ~5 k WSPM) .....                                 | 16 |

| RefFab Academy (training ecosystem) .....                                                         | 17 |

| Packaging-First tracks and test .....                                                             | 18 |

| Mobilisation, attraction & retention .....                                                        | 19 |

| Trusted personnel & compliance (people component of Comply-to-Connect) .....                      | 19 |

| KPI set and learning curves .....                                                                 | 19 |

| Economic leverage and industrial-policy benefits .....                                            | 20 |

| Financing and preliminary timeline .....                                                          | 22 |

| Investment costs (CAPEX) .....                                                                    | 22 |

| Operating costs (OPEX) .....                                                                      | 23 |

| Validation via comparison projects .....                                                          | 24 |

| Financing and institutional anchoring .....                                                       | 25 |

| Governance and openness management .....                                                          | 27 |

| Ownership, operation, mandate .....                                                               | 27 |

| Blueprint governance (open-source model) .....                                                    | 27 |

| Certification, label, and quality .....                                                           | 28 |

| Transparency vs security & export control .....                                                   | 28 |

| Co-operation—yes; voluntary and competition-law compliant .....                                   | 28 |

| EU integration and programme alignment .....                                                      | 28 |

| Dispute resolution and escalation .....                                                           | 29 |

| Continuity, measurability, learning loops .....                                                   | 29 |

|                                                                    |    |

|--------------------------------------------------------------------|----|

| Communications and stakeholder strategy (cross-cutting) .....      | 29 |

| RefFab as public infrastructure: mandate and state commitment..... | 30 |

| Risks and mitigations.....                                         | 31 |

| International context .....                                        | 33 |

| Conclusion and outlook.....                                        | 33 |

# Transparent Reference Fab for Europe: Open, scalable semiconductor manufacturing as a strategic concept

## Executive Summary

Europe faces, in 2025, the existential task of strengthening its technological sovereignty in semiconductor manufacturing. The European Chips Act of 2022 set the goal of increasing Europe's share of global chip fabrication by 2030 from under 10% to 20%—an ambitious undertaking intended to mobilise a total of around 43 bn € in investment<sup>1</sup>. Meanwhile, all 27 EU Member States, under a Semicon Coalition, are calling for an evolution towards a “Chips Act 2.0”. Rather than focusing on market share alone, this aims to close critical gaps: availability of key technologies is to be secured, as well as procedures permitting acceleration, and a deepening of competencies along the entire microelectronics value chain<sup>2</sup>. In parallel, the EU Agency for Cybersecurity (ENISA) warns of increasing cyberattacks on critical infrastructures—a wake-up call that trustworthy, auditable hardware has become a security imperative. Worldwide, other industrial nations are pushing ahead with semiconductor expansion: Japan is investing billions in the Rapidus initiative (target: 2-nm mass production by 2027)<sup>3</sup>, and the United States launched the CHIPS and Science Act (52 bn \$), followed by major investments such as Texas Instruments' plan exceeding 60 bn \$ for new fabs in Texas and Utah<sup>4,5</sup>. China, too, has been flooding the sector with subsidies for years to build domestic fabs. Within Europe, there are isolated initiatives—e.g., Ireland's “Silicon Island” strategy (national semiconductor offensive since 2025)<sup>6</sup>, the Swiss “Chip FabLab” project co-led by ETH Zurich<sup>7</sup>, or plans around CSIC/CNM in Spain. These individual efforts matter but, lacking critical mass, cannot solve the root problem. Europe must consolidate its strategy and act as one to be

---

<sup>1</sup> [https://commission.europa.eu/strategy-and-policy/priorities-2019-2024/europe-fit-digital-age/european-chips-act\\_en](https://commission.europa.eu/strategy-and-policy/priorities-2019-2024/europe-fit-digital-age/european-chips-act_en)

<sup>2</sup> <https://digital-strategy.ec.europa.eu/en/news/semicon-coalition-calls-reinforced-chips-act>

<sup>3</sup> <https://www.rapidus.inc/en/tech/te0006>

<sup>4</sup> <https://bidenwhitehouse.archives.gov/briefing-room/statements-releases/2022/08/09/fact-sheet-chips-and-science-act-will-lower-costs-create-jobs-strengthen-supply-chains-and-counter-china>

<sup>5</sup> <https://www.ti.com/about-ti/newsroom/news-releases/2025/texas-instruments-plans-to-invest-more-than--60-billion-to-manufacture-billions-of-foundational-semiconductors-in-the-us.html>

<sup>6</sup> <https://enterprise.gov.ie/en/publications/silicon-island-a-national-semiconductor-strategy.html>

<sup>7</sup> <https://ee.ethz.ch/news-and-events/d-itet-news-channel/2025/08/boosting-swiss-semiconductors-plans-for-chip-factory-gain-media-attention.html>

prepared against geopolitical risks, supply bottlenecks, and technological lag. Against this background, this paper presents the concept of a Transparent Reference Fab (TFR) as a proactive response and as a **piece of public-interest manufacturing infrastructure**.

The Transparent Reference Fab for Europe is a proposed reference semiconductor plant designed to be open, scalable, and production-ready. It serves as an open-source blueprint for the rapid build-out of additional fabs in Europe. Core principles of this approach are:

- **Series-capable manufacturing model instead of a pilot line:** Unlike typical pilot lines (which often have a demonstration character and, at best, capacities for small-series production), the Reference Fab is designed from the outset for industrial volumes and 24/7 operation. It is intended to shoulder real production loads and operate economically, so that any plant copied from this model is production-ready from day one and does not require a costly transition from pilot to series production. The dimensioning is expressed not as a single figure but as a capacity corridor on the order of a few thousand 300-mm wafer starts per month; the exact operating point will be refined and validated in Phase 0 together with anchor customers and partners.

- **Transparent open-source blueprint:** All key processes, equipment parameters, and fab operations are, in principle, openly documented and made accessible for re-use. This transparency allows European industrial actors and states to use the fab as a blueprint to build new plants autonomously with lower development risk. It also creates trust in the chips produced: security-relevant semiconductors can be examined down to the process level, ensuring **trustworthy electronics “Made in Europe”**. Any backdoors or manipulations are significantly harder to conceal in a transparent manufacturing process. Based on open design kits and reproducible, auditable toolflows (CI/CD) and reference IPs are provided openly; this measurably lowers entry barriers and audit times. The project thus aims for the **“Trustworthy EU Fab Network”** label—Independent bodies should **certify the trustworthiness** of production on the basis of the open documentation and inspections – from the manufacturing process up to the manufactured Chip.

- **Integrated Chiplet, packaging and test flow:** Performance, energy, reliability, and security targets are now decided in the back end/SiP/SoP. Therefore, advanced packaging is a core component from day 1: **Co-packaging of leading-edge compute dies** with 65-nm periphery (PMIC, mixed-signal, sensor IF or trust anchors), puts the last stage of **trustworthy manufacturing back to Europe**. We anchor chiplet standards (e.g., UCle/BoW/OpenHBI), design-for-packaging, and qualified test flows. In this way, we do not widen the gap to the leading edge but **bridge the gap systemically**. Close exchange with EU-funded pilot lines (e.g., APECS) is required here. The Reference Fab is thus conceived as an **integrated front-end + packaging + test environment**, not as a packaging-only project.

- **Focus on 65-nm CMOS as a strategic technology node:** The Reference Fab targets the established 65-nm node, as it will be in demand for a long time and as it is sufficiently performant for many critical applications. Sectors such as automotive, industrial, med-

tech and aerospace can manufacture their microcontrollers, ASICs and mixed-signal components at 65 nm—robustly, cost-effectively, and in high volumes. Forecasts indicate that even after 2030, a significant share of global chip demand will fall to technologies  $\geq 65$  nm (especially analogue/power electronic chips), while  $< 10$  nm will account for only  $\sim 12\%$ . As a bridging technology, operations will initially start on the proven 130-nm node, for which equipment and open process data and PDKs are immediately available in Europe. This bridging approach enables a rapid start of production with high yield, while the 65-nm line is ramped in parallel to maturity. The fab infrastructure is designed modularly so that a later upgrade to 65 nm (or smaller) is possible without fundamental replanning. The focus initially remains on 65 nm as the “sweet spot” between maturity, availability, and sovereignty gains. Importantly, selected platforms will be assured long-term availability (target corridor  $\geq 15$  years) with obsolescence pathways; certification and qualification pathways (e.g., AEC-Q100/IEC 61508/DO-254) are part of the offering. This **explicitly avoids a commodity-volume** model and instead pursues a trusted-premium approach with service and quality premiums. A key value adding comes from the advances system integration See previous point (Integrated Chiplet, packaging and test flow)

- **Data-driven manufacturing, audit trails & automation:** Dense inline metrology, SPC/ML-assisted control, and end-to-end feedback from front-/back-end data shorten ramp-ups and create verifiable quality and trust metrics; this also includes robotics-based automation processes. Where sensible, selective single-wafer steps are used; furnace/batch processes remain economical.

- **Use of existing resources and expertise:** The Reference Fab should be located in close physical proximity to existing research and pilot lines such as IHP, CEA-Leti, or imec in order to translate existing process know-how directly into industrial implementation. This proximity enables a significantly accelerated ramp-up, as established teams, qualified equipment, and proven process modules can be used directly. At the same time, the Reference Fab remains institutionally independent—it is not an extension of a research institution but an industrial Reference Fab with its own mandate. RTOs and pilot lines remain the place where new materials, device concepts and process bricks are developed; the TRF industrialises mature bricks and turns them into standardised, auditable modules within a trusted manufacturing environment. By **purposefully integrating research know-how into an open production model**, Europe can become operational more quickly without starting from zero.

- **Governance & public-trust mandate:** There are several options, e.g. public ownership, PPP or a public-trust mandate—institutionally independent of R&D institutions, with physical proximity/co-location; non-discrimination, open audit interfaces (traceability down to lot/wafer level), clear access rules; industry co-investments in equipment/packaging. This ensures replicability, planability, and verifiable trust mechanisms. **The Fab is conceived as public-interest infrastructure.**

- **Talent, training & trusted personnel (RefFab Academy):** The TRF embeds qualification as a core task through a RefFab Academy that provides core curricula, European Qualifications Framework -aligned micro-credentials and a digital Skills-Passport linked to role-based access control and “comply-to-connect” mechanisms in the MES. Training follows the TRF’s workflow – manufacturing, chiplet integration, advanced packaging and test – and is delivered via standardised Learning Cells and a “learning-workshop-in-a-box” for on- and off-the-job formats. Dual vocational and higher-education pathways are connected through memoranda of understanding, and rotations between the TRF network, OSAT & RTO partners, shorten time-to-competence. Active recruiting in Europe and beyond, reskilling and international hiring are combined with family-ready conditions such as shift-compatible childcare, language tracks, mentoring and a Just-Culture approach. Proportionate, risk-based background checks under the EU General Data Protection Regulation and a compliance gate for competition, foreign investment, dual-use, intellectual property and privacy safeguard publications and technical artefacts. Open design kits and EDA tools, together with freely available reference designs, documented manufacturing flows and toolchains, remain the instructional foundation. Talent dimensioning is likewise expressed not as a single figure but as a training corridor on the order of several dozen engineers and around one hundred technicians and operators to be trained per site and year in the build-up phase; the exact intake, skill mix and steady-state levels will be refined and validated in Phase 0 with regional education partners and anchor employers.

- **Scalable reference solution & network concept:** The overarching goal is a multiplicative effect: the Reference Fab serves as a blueprint that can be copied one-to-one and rolled out across several European regions. Each new fab built to this model immediately increases regional manufacturing capacity and supply-chain resilience. By standardising the architecture, even production lots and personnel can be exchanged between sites. If a fab fails in a crisis situation, others with identical equipment can temporarily step in—improving supply security. Such a network of identical, trustworthy fabs would reduce Europe’s dependence on non-European suppliers while also serving as a platform for innovation (e.g., joint further development of new process modules, open IP libraries). The decision where and when to build additional sites remains policy- and demand-driven; the Reference Fab primarily validates the blueprint, governance and workforce model. Potential Fab clones can be driven by private companies and operated at higher volumes making use of the blueprint.

- **Specialisation for niche products:** Multiple fabs with an identical CMOS base can purposefully differentiate themselves through process-modular add-ons (e.g., RF, power, sensor modules, photonics)—without changing the base technology. In this way, we combine economies of scale with technological differentiation in higher-margin niches. The result is a flexible manufacturing ecosystem that promotes both innovation and specialisation in niche markets.

- **Demand anchors:** Public procurement (critical infrastructure, public administration, security, defence and space) secures a strategic base load in terms of guaranteed use cases, while trusted standard building blocks (e.g. secure controllers, gateways, mixed-signal hubs) and a dense SME-driven system-in-package (SiP) ecosystem are expected to generate most of the volume within the TRF capacity corridor on the order of a few thousand 300-mm wafer starts per month. Industry co-investments expand packaging and test capacities. Delineation: no EUV or leading-edge foundry, no commodity volume model — focus on trusted-premium manufacturing, SiP/chiplets and long product life cycles.

- **Financing & economic viability (brief overview):** The business model is built around a public-mission infrastructure operator with mixed public and private funding. Options include public-private partnership structures or publicly owned entities with long-term industrial co-investments and base-load contracts, combined with a subsidised share of CAPEX from site-level and EU programmes and staged funding tied to milestones (MPW start, 65-nm ramp-up, packaging pilot). The revenue mix would combine foundry, packaging and test, and value-added services (MPW, certification, obsolescence management). The TRF is framed as critical infrastructure with a clear public mission, not as a purely speculative stand-alone foundry project.

- **Guardrails (without hard promises):** MPW offers  $\geq 4/\text{year}$  (130 nm) &  $\geq 2/\text{year}$  (65 nm), SiP-MPW from Year 2; packaging targets: RDL pitch  $10 \rightarrow \leq 5 \mu\text{m}$ , microbump  $\leq 55 \mu\text{m}$ ; long-term supply  $\geq 15$  years; trust KPIs: published yield/DPPM & traceability metrics.

**Perspective 2040+:** The relevance of  $\geq 65\text{-nm}$  classes will persist well beyond the 2030s due to analogue/mixed-signal content, power electronics, eNVM MCUs, RF front-ends, rad-hard/space electronics, and security requirements. Long-lifecycle industries (automotive/automation/med-tech/aerospace) and chiplet architectures further stabilise demand: 65 nm takes on peripheral functions, sensing, PMIC, safety MCU, while leading-edge compute is integrated via co-packaging. The network can—where sensible—shrink modularly or expand its SiP/OSAT footprint without changing the business model.

This Executive Summary addresses policymakers at EU and national level as well as potential funders in public administration and industry. It outlines, in compact form, the vision of a Transparent Reference Fab and its benefits. The recommendation is to advance this strategic concept swiftly with political backing and initial funding. In view of the ongoing reform efforts around the Chips Act, the heightened threat environment, and global investment dynamics, now is the right moment to lay the foundations for open and sovereign semiconductor manufacturing in Europe.

**Note (disclaimer):** This paper presents a concept and sketches initial proposals for implementation and financing. Delivering a robust realisation will require deeper analysis and a detailed execution plan. Developing these is an integral part of the concept and the subject of Phase 0.

### Assumptions, Scope & Non-Goals

- This paper proposes a replicable TRF blueprint (scope, capabilities, governance, training) — not a site decision or an investment commitment.

- Core focus: packaging-first manufacturing (system-in-package, redistribution layers and fan-out) with co-integration to leading-edge nodes, test (ATE/SLT), open design-kit/EDA integration, auditability and workforce pipelines.

- Technology path: 130 nm and 65 nm as evergreen nodes for analogue/mixed-signal, microcontrollers, power-management ICs, RF and IoT; concrete volumes and product mixes are partner- and site-specific.

- Complementary to leading-edge fabs; targets resilience, qualification and SME access, not commodity volume competition.

- Implementation is phase-gated (Phase 0 → Go/No-Go) with measurable milestones, including validation of capacity and talent corridors.

- Quantitative figures (capacity, talent, CAPEX ranges) are scenario-based orders of magnitude; all numbers are indicative and subject to partner due diligence and site-specific design in Phase 0.

## About the Authors:

**Norbert Herfurth** earned his PhD (TU Berlin, 2020) in semiconductor failure analysis. 2013–2019 he worked in TU Berlin’s Semiconductor Devices group. Since 2020 at IHP—initially as cross-department postdoc/project coordinator, now research group lead. He initiated and still shapes IHP’s open-source activities, including Europe’s first open-source PDK. Currently he focuses on open source hardware and chiplet integration ecosystems.

Current employment is for identification only; views are personal.

Contact: [ref-fab@hep-alliance.org](mailto:ref-fab@hep-alliance.org)

**Arnd Weber** is an economist and sociologist. Until retirement he was researcher at KIT, advising the EU Commission, EU Parliament and German government. His PhD traced the rise of public-key cryptography; he co-designed untraceable, loss-tolerant e-money, analysed the Dresden semiconductor cluster, and in 2003 predicted issues in European mobile data services. He founded “Quattro S” and helped initiate the HEP project on an open hardware security module. Currently he is subcontractor to IHP for the SIGN-HEP project (information is for identification only; views are personal). Contact: [arnd.weber@alumni.kit.edu](mailto:arnd.weber@alumni.kit.edu)

**Steffen Reith** is Professor of Theoretical Computer Science at RheinMain University of Applied Sciences in Wiesbaden. During his work at Elektrobit Automotive, he developed products with cryptographic functions for use in current automobiles.

Contact: [Steffen.Reith@hs-rm.de](mailto:Steffen.Reith@hs-rm.de)

**Anna Herfurth** is Head of Human Resources at IHP. She brings over six years of leadership experience in strategic HR, organizational development, and digital transformation. At IHP, she drives talent development, employer branding, and workforce structures for a high-tech research environment. In the Reference Fab initiative, she contributes expertise in HR strategy, skills pipelines, and dual education models for the semiconductor industry.

Current employment is for identification only; views are personal.

**René Scholz** earned a PhD in physics (MLU Halle-Wittenberg, 1999) after research on point-defect diffusion in Si and GaAs at the Max Planck Institute of Microstructure Physics. He joined IHP in 2001 for RF characterization and modeling, later leading the MPW Service and PDK development. He also holds an MBA (European University Viadrina, 2008). Recently, he contributes to IHP’s open-source BiCMOS PDK.

Current employment is for identification only; views are personal.

[www.linkedin.com/in/rene-scholz-86b4473](https://www.linkedin.com/in/rene-scholz-86b4473)

**Torsten Grawunder** is a hardware/security engineer. He studied physics of electronic components at TU Chemnitz, specializing in ASIC design for communication technology. Since 2021 he has worked at Swissbit Germany AG in system design/embedded solutions (APATS), creating and analyzing pre-development system concepts for future NAND-flash products and coordinating Swissbit’s funding processes. Previously, for 20+ years, he developed encryption hardware for ISDN, ATM and Ethernet at Biodata, secunet and Rohde & Schwarz SIT.

Contact: [torsten.grawunder@swissbit.com](mailto:torsten.grawunder@swissbit.com)

## List of Abbreviations (Executive Summary)

### Abbreviation Meaning

|               |                                                                     |

|---------------|---------------------------------------------------------------------|

| <b>ADK</b>    | Assembly Design Kit                                                 |

| <b>AMS</b>    | Analogue and Mixed-Signal                                           |

| <b>ATE</b>    | Automated Test Equipment                                            |

| <b>CAPEX</b>  | Capital Expenditure                                                 |

| <b>CD/CI</b>  | Continuous Deployment / Continuous Integration                      |

| <b>ENISA</b>  | European Union Agency for Cybersecurity                             |

| <b>EQF</b>    | European Qualifications Framework                                   |

| <b>FDI</b>    | Foreign Direct Investment                                           |

| <b>IP</b>     | Intellectual Property                                               |

| <b>IQ/OQ</b>  | Installation Qualification / Operational Qualification              |

| <b>KRITIS</b> | Critical Infrastructure (German: <i>Kritische Infrastrukturen</i> ) |

| <b>LTAs</b>   | Long-Term Agreements                                                |

| <b>MES</b>    | Manufacturing Execution System                                      |

| <b>ML</b>     | Machine Learning                                                    |

| <b>MoU</b>    | Memorandum of Understanding                                         |

| <b>MPW</b>    | Multi-Project Wafer                                                 |

| <b>OPEX</b>   | Operational Expenditure                                             |

| <b>OSAT</b>   | Outsourced Semiconductor Assembly and Test                          |

| <b>PDK</b>    | Process Design Kit                                                  |

| <b>PMIC</b>   | Power Management Integrated Circuit                                 |

| <b>PPP</b>    | Public–Private Partnership                                          |

| <b>RBAC</b>   | Role-Based Access Control                                           |

| <b>RDL</b>    | Redistribution Layer                                                |

| <b>SiP</b>    | System-in-Package                                                   |

| <b>SLT</b>    | System-Level Test                                                   |

| <b>SoC</b>    | System-on-Chip                                                      |

| <b>SoP</b>    | System-on-Package                                                   |

| <b>SPC</b>    | Statistical Process Control                                         |

| <b>SPV</b>    | Special Purpose Vehicle                                             |

| <b>TRF</b>    | Transparent Reference Fab                                           |

| <b>UCle</b>   | Universal Chiplet Interconnect Express                              |

| <b>VET</b>    | Vocational Education and Training                                   |

| <b>WSPM</b>   | Wafer Starts per Month                                              |

## Starting point: sovereignty under new conditions

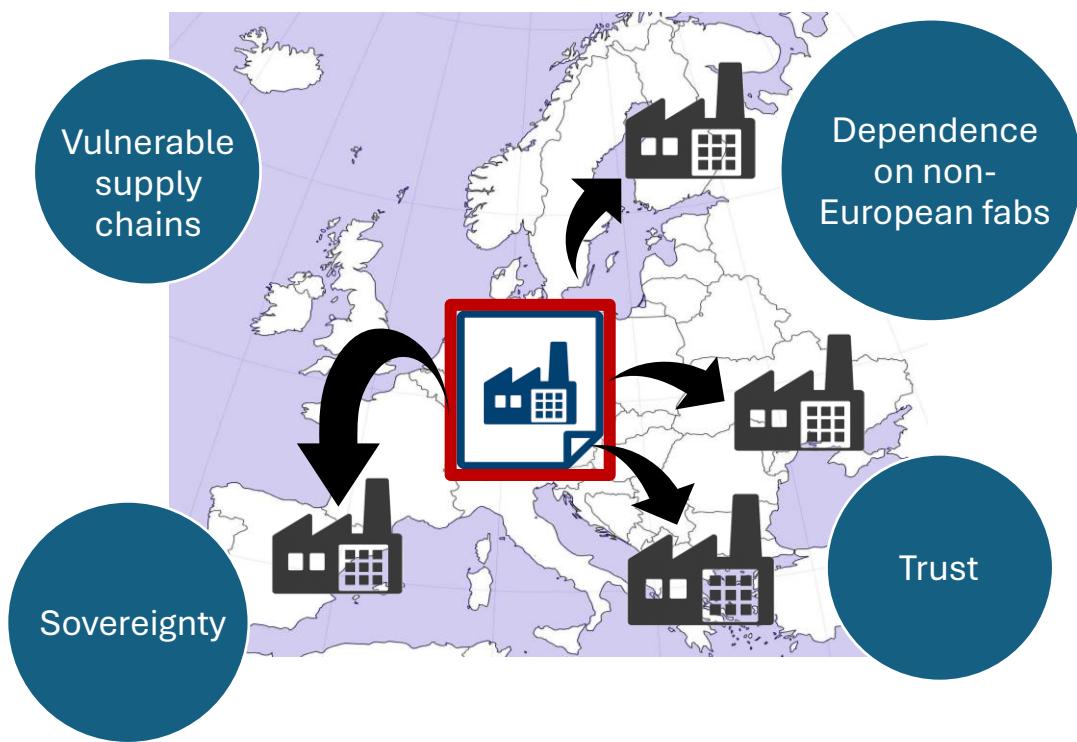

Over recent decades, Europe has lost substantial ground in semiconductor manufacturing. At present, less than 10% of global chip production is accounted for by European fabs. High-value microelectronics largely originate from Asia or the United States—particularly at the leading edge, Europe is almost entirely dependent on imports. Over 80% of advanced chips used in areas such as AI, telecommunications, med-tech, or defence must be imported from the United States or East Asia<sup>8</sup>. This concentration is not only an economic issue but also a strategic risk: supply disruptions (for example, due to geopolitical tensions around Taiwan) could paralyse essential industries. The COVID-19 pandemic and subsequent chip crises painfully exposed the vulnerabilities of global supply chains.

Against this backdrop, the EU adopted the European Chips Act in 2022 to counteract these trends. The official goal was to double Europe's global market share to 20% by 2030—with public incentives and regulatory facilitations intended to trigger investments of over 40 bn €. In practice, an investment wave has indeed been set in motion, yet doubts are growing about achieving the 20% target. The European Court of Auditors (ECA), for instance, considers the target excessive and unrealistic—it forecasts that, without a course correction, Europe will account for only around 12% of global value creation in the chip industry by 2030<sup>9</sup>. Accordingly, all EU Member States and industry associations are now pushing for a “Chips Act 2.0”: the revision should set clear priorities for where and why Europe must lead in future, rather than merely aiming at an aggregate market share.

At the same time, the threat landscape is intensifying: ENISA and others warn that attacks on digital infrastructure are increasingly targeting hardware vulnerabilities and supply chains. Without trustworthy domestic manufacturing, Europe could become a vulnerable single point of failure in the global technology system. Hardware security “by design”—for example through transparent, auditable production processes—has become the order of the day.

Internationally, there is an intense race for semiconductor capacity. In addition to its 52 bn \$ support package, the United States has already seen concrete mega-projects: Texas Instruments is investing over 60 bn \$ in seven new fabs in Texas and Utah, while Intel, TSMC, and Samsung are building “megafabs” in Arizona, Texas, and across the US Rust Belt. China has for years subsidised tens of billions for new plants. Japan has formed Rapidus, a consortium (including Toyota, Sony, SoftBank) aiming—with state support (planned 5 tn ¥, approx. 33 bn € required)—to produce 2-nm chips in series from 2027<sup>9</sup>.

Europe, too, has recently announced several lighthouse projects: for example, STMicroelectronics and GlobalFoundries are jointly investing in a new 300-mm FD-SOI fab

---

<sup>8</sup> [https://www.eca.europa.eu/ECAPublications/SR-2025-12/SR-2025-12\\_EN.pdf](https://www.eca.europa.eu/ECAPublications/SR-2025-12/SR-2025-12_EN.pdf)

<sup>9</sup> <https://www.reuters.com/technology/tsmc-begins-producing-4-nanometer-chips-arizona-raimondo-says-2025-01-10/>

in Crolles (France)—with ~7.5 bn € in costs planned, of which ~2.9 bn € publicly funded<sup>10</sup>. However, this project was put on hold in mid-2025 due to cyclical headwinds<sup>11</sup>. In Germany, with TSMC as technology leader, the European Semiconductor Manufacturing Company (ESMC) is being built in Dresden. Over 10 bn € is to be invested; in August 2024 the EU approved 5 bn € in funding<sup>12</sup>. This first European TSMC fab (planned for 28/22-nm automotive technology) is to go into production by 2027 at the latest<sup>13</sup> and reach full capacity by 2029<sup>14</sup>. The project is celebrated as a milestone, yet its scope also underlines the challenge: it ties up enormous resources and primarily addresses the 22-nm segment; for truly security-critical nodes >65 nm it brings little direct benefit. Meanwhile, Intel, after protracted wrangling over subsidies, completely cancelled its originally larger project in Magdeburg (~€30 bn for 4/3-nm fabs) in July 2025<sup>15</sup>.

In summary, the starting position shows an acute need for new, complementary strategies beyond the previous focus on the very finest nodes. Europe requires additional manufacturing capacity in pertinent technology domains away from the leading edge—and this capacity must be trustworthy, resilient, and rapidly multipliable. This is precisely where the concept of the **Transparent Reference Fab (TRF)** comes in, as elaborated below. It is conceived as a response to sovereignty deficits, security risks, and market gaps in the “legacy” segment, without losing sight of linkages to state-of-the-art developments (chiplets/packaging). Instead of isolated stand-alone solutions, it offers a European, coordinated reference approach.

A concise example illustrates the added value of acting together: applied to the EU, it would be more efficient to develop a scalable reference model that is then replicated at multiple sites, rather than each country building a small semiconductor line in isolation. National solo efforts may yield a short-term boost in local competence but risk duplication of work and fragmentation of resources. An EU-wide reference model—the Transparent Reference Fab—could counteract this by developing best practices centrally and then rolling them out locally. Initiatives already planned (for example in Ireland, Spain, or Switzerland) could be harmonised if they built on the TRF’s open documentation and became part of a European network. Rather than operating in separate silos, these pilot projects could thus serve as the first nodes in a European federation and benefit from joint developments. Europe-wide coordination would also increase political clout—instead of many small voices, a concerted approach to funding and industry partnerships would emerge. National initiatives demonstrate Europe’s strong willingness to rebuild its own

---

<sup>10</sup> <https://gf.com/gf-press-release/globalfoundries-and-stmicroelectronics-finalize-agreement-for-new-300mm-semiconductor-manufacturing-facility-in-france/>

<sup>11</sup> <https://bits-chips.com/article/st-gf-fdsoi-fab-paused-among-market-headwinds/>

<sup>12</sup> [https://ec.europa.eu/commission/presscorner/detail/en/ip\\_24\\_4287](https://ec.europa.eu/commission/presscorner/detail/en/ip_24_4287)

<sup>13</sup> <https://pr.tsmc.com/english/news/3049>

<sup>14</sup> [https://ec.europa.eu/commission/presscorner/detail/en/ip\\_24\\_4287](https://ec.europa.eu/commission/presscorner/detail/en/ip_24_4287)

<sup>15</sup> <https://www.heise.de/en/news/Intel-gives-up-Magdeburg-fab-and-announces-end-of-foundry-10499170.html>

manufacturing capacity. To unlock the full potential, however, these efforts should be coordinated and designed for scale. The TRF concept provides a proposal for this: it can serve as a reference framework to interconnect national projects as parts of a larger whole. In this way, a scalable, EU-wide model emerges instead of many isolated pilot factories—more efficient and more resilient in the long term. As a representative of ETH Zurich aptly put it, “it is more cost-efficient to consolidate infrastructure than to operate numerous replicated versions within the country”<sup>16</sup>. This principle can be applied to Europe as a whole to turn fragmentation into alignment.

**Conclusion on the starting position:** The need for a new, complementary strategy is evident. Europe requires additional semiconductor manufacturing in key technology areas beyond the very finest structures—and it must be trustworthy, resilient, and rapidly multipliable. This is precisely where the concept of the Transparent Reference Fab comes in: as a response to the sovereignty gaps, security risks, and market weaknesses outlined in the realm of established technologies, and as a driver of innovation for new forms of cooperation and openness in microelectronics.

## Objectives of the concept

The vision of the **Transparent Reference Fab (TRF)** pursues two overarching objectives:

- (1) the rapid multiplication of European semiconductor fabs, and

- (2) the assurance of trustworthy production for safety-critical applications.

To achieve these guiding objectives, the concept follows several interlinked sub-objectives:

- **Strengthen technological sovereignty:**

Europe should be enabled to manufacture essential chips autonomously—especially those required in critical infrastructures, the military, or strategic industries. This independence from non-European suppliers increases resilience to geopolitical tensions, export restrictions, or deliberate supply cut-offs.

A key lever is the rapid build-out of additional manufacturing capacity at established technology nodes ( $\geq 65$  nm). Chips in this segment—such as microcontrollers, mixed-signal ASICs, or sensor SoCs—are central to many industrial applications and have recently often been a bottleneck in Europe.

- **Multiplier for new fabs:**

The TRF serves as a reference model that investors and industry can use as a proven blueprint for additional plants. The open blueprint lowers entry barriers for consortia or companies considering their own fab. Every euro of public seed funding into the TRF can mobilise a multiple of private follow-on investment (multiplier effect). Over time, this

---

<sup>16</sup> <https://ee.ethz.ch/news-and-events/d-itet-news-channel/2025/08/boosting-swiss-semiconductors-plans-for-chip-factory-gain-media-attention.html>

creates a network of like-for-like fabs with compatible architecture and process bases—sharing common standards and learning from one another.

- **Increase the trustworthiness of electronics:**

A central goal is to build a trustworthy supply chain for electronics “made in the EU”. From the production equipment and process know-how to the finished chip, end-to-end auditability should be ensured. The aim is a “**Trustedworthy EU Fab Network**” label, awarded by independent bodies on the basis of transparent documentation and regular audits. Safety-critical applications—from power grids to space—can thus rely on certified, verifiable hardware.

- **Strengthen European networking and resilience:**

The TRF is the starting point for a Europe-wide network of interoperable fabs. Standardised processes and equipment enable mutual backup in crises (failover capability), the exchange of personnel or lots, and joint further development. This raises supply security and reduces systemic dependencies.

- **Establish an open innovation and training ecosystem:**

By openly providing process knowledge (open technology), PDKs, reference designs, and even bills of materials (BOMs), an innovation-friendly environment emerges. Universities, start-ups, and SMEs can plug in directly, develop new designs, or contribute process modules. The fab becomes a practical learning site for students, professionals, and career-changers. In combination with the **RefFab Academy**, a training infrastructure is created that specifically qualifies personnel for packaging, test, data analytics, and fab operations. As in open-source software, collaboratively developed improvements enhance the competitiveness of the entire network.

- **Enable a sustainable business model:**

In the long term, the resulting fabs should operate on a commercially sound basis, ideally without permanent subsidies.  The focus is on market segments where quality, trust, and long-term availability command price premia—for example automotive, aerospace, or safety-critical IT. “**Trustworthy** chips” from European fabs should establish themselves as a premium product with added value. At the same time, these fabs are part of European infrastructure. This requires a baseline public commitment to safeguard strategic capacity—e.g., via public demand (critical infrastructure), moderate modernisation grants, or regulatory stability. The concept targets a **hybrid model**: market-viable in normal operation, with flanking public backstops in critical phases.

Thus, a hybrid model emerges—**commercially viable in steady state, with public backing as part of Europe’s public-service provision**.

In summary, these objectives are tightly interwoven: technological sovereignty builds trust; trust is a precondition for market acceptance; and market success attracts new investors, easing the network’s expansion. The TRF therefore addresses **security and scaling in equal measure**—a differentiator compared with conventional fab projects. The TRF is

more than a production site: it is a strategic lever for Europe's sovereignty, innovative capacity, and trust gains in global competition.

## Technological roadmap: from pilot to network fab

Building a European **Reference Fab** is a technically and administratively highly complex undertaking. The following roadmap sets out an ambitious yet realistically achievable timeline, grounded in experience from European semiconductor projects. It accounts for regulatory procedures, technological development paths, and parallel acceleration measures. The planning conservatively assumes framework conditions in Germany—deliberately chosen as a robust reference case for permitting and infrastructure matters.

### Phase 0 – Feasibility studies and consortium formation (9–15 months)

In this initial phase, the concept, partners, and governance structure are finalised. This includes site analyses (including local construction and environmental requirements), a robust cost estimate, personnel demand and competence analyses, the set-up of a training network, and the definition of the fab architecture including packaging and test infrastructure (e.g., RDL, interposer, SLT/ATE). Proximity to existing research facilities (e.g., IHP, CEA-Leti, imec) is deliberately sought—while maintaining clear institutional independence.

All time and financial figures in the concept are preliminary assumptions and will be validated, prioritised, and specified in this phase.

**Target state for Phase 0:** Consortium, site decision, financing model, and governance draft are agreed, including a defined scope for integrated packaging from the start of production.

### Phase 1 – Construction of the Reference Fab and parallel process development (30–36 months)

#### Part 1: Planning, permitting, and construction of the fab (24–30 months)

Following completion of the feasibility study, the construction and equipment phase begins. Typical permitting procedures (e.g., under the Federal Immission Control Act—BImSchG—and environmental requirements) are taken into account. To save time, an existing or expandable cleanroom site (brownfield) should be used. The fab is designed from the outset with 300-mm equipment and 65/(55)-nm-capable tools. Space, utilities, and equipment layouts for back-end processes (advanced packaging) are already considered in the base architecture. The concurrent build-up of a packaging zone with chiplet, RDL, fan-out, and interposer capabilities is part of the fab design.

**Target state, Part 1:** Cleanroom structures, utilities, and main tools are installed and qualified.

#### Part 2: Parallel process and documentation preparation (30–36 months)

In parallel, existing process recipes for 130 nm are consolidated in partner lines (e.g., IHP,

CEA-Leti, imec) and prepared for 65 nm. The aim is a modular documentation package for the subsequent open-source blueprint. In close coordination with partners, test flows (e.g., KGD → SLT) and packaging-specific process modules are developed, standardised, and qualified. Initial packaging test structures (UCle, BoW, OpenHBI) are prepared. In addition, this phase launches the concrete design of the **RefFab Academy**: training plans, qualification profiles, and initial learning modules for technicians and engineers are developed.

**Target state, Part 2:** Complete process documentation for 130 nm; validated pre-versions for 65 nm are available.

## Phase 2 – Commissioning of the Reference Fab (9–12 months)

After installation and qualification, production ramp-up starts on 130 nm. Initial test and functional chips are fabricated. Operations simultaneously serve as a proof-of-concept for the transparency principle: MES parameters, yield data, and quality indicators are documented and (to the defined level of transparency) published. In parallel with the ramp, a first packaging test design (e.g., PMIC + test logic) is manufactured and qualified at interposer level. Integration into MES and quality documentation follows the same transparency principles. From this phase onward, the fab is prepared for a certification model under the planned “**Trusted EU Fab Network**” label, which can be validated by third-party assessors along defined transparency pathways.

**Target state for Phase 2:** Industrially usable 130-nm PDK with test chips and audit documentation is published, plus a verified packaging demonstrator with a documented process route.

## Phase 3 – Technological shrink to 65 nm / 55 nm (24–30 months)

Migration to the target 65-nm node begins. Complementary tool upgrades and the transfer of prepared recipes proceed step by step. Multi-project wafers validate the PDK and support yield optimisation. A 55-nm variant can be trialled in parallel. The packaging flows prepared in Phase 2 are now geared towards co-packaging with 65-nm periphery and leading-edge logic. Yield optimisation, thermal simulations, and validation of standard interfaces (e.g., UCle) are carried out in an integrated manner with the 65-nm ramp-up. Long-term availability (e.g., over  $\geq 15$  years) and application-oriented certifiability (AEC-Q100, ISO 26262, IEC 61508, etc.) are technically prepared already in this phase.

**Target state for Phase 3:** Qualified 65-nm process with open PDK, documented yield, and optional co-packaging trial run, plus a qualified co-packaging test chip (SiP or interposer integration) with documented yield and SLT report.

## Phase 4 – Networking, scaling, and consolidation (from Year 7–11)

The Reference Fab now serves as a blueprint for additional sites in Europe. First clone fabs are established—ideally based on identical architecture, processes, and PDKs. At the same time, the Reference Fab assumes training and support functions for new teams. The fab’s packaging know-how is published as a design-for-packaging guide and integrated into

MPW offerings. New fabs adopt validated packaging flows and adapt them to regional application domains (e.g., sensor integration, med-tech, defence). Access to the fab and MPW services is non-discriminatory and based on transparent access rules (Open Foundry principle).

Structurally, a network of interoperable fabs with shared governance emerges:

- **Community organisation:** coordination of quality, exchange, and further development

- **Open platform:** maintenance and extension of the open process blueprint

- **Audit and certification structure:** adherence to common standards

- **Site diversity:** inclusion of strong clusters (e.g., Dresden, Grenoble, Eindhoven) and structurally weaker regions

**Target state for Phase 4:** At least three fab sites actively use the reference architecture; community structures and certified processes are established.

### Overall timeline

| Phase     | Period (from project start) | Duration [months] | Target state                                        |

|-----------|-----------------------------|-------------------|-----------------------------------------------------|

| Phase 0   | H2 2026–2027                | 9–15              | Consortium, site, and financing agreed              |

| Phase 1.1 | 2027–end of 2029            | 24–30             | Construction & tool installation completed          |

| Phase 1.2 | 2027–early 2030             | 30–36             | Process & documentation baseline for 130 nm / 65 nm |

| Phase 2   | 2030–2031                   | 9–12              | 130-nm PDK released; production started             |

| Phase 3   | 2031–2033                   | 24–30             | 65-nm reference manufacturing validated             |

| Phase 4   | from 2031 onwards           |                   | long-term Network & clone fabs in rollout           |

**This plan includes conservative buffers** for permitting, tool availability, and process iterations. With political prioritisation, a complete blueprint project cycle can be achieved within **8–11 years**.

### Technological guidelines for the fab

Across all phases, the following architecture principles apply:

- **Industrial-grade scalability:** Base module for approx. **5,000 wafer starts per month**; expandable by additional modules to **10,000+**.

- **Modern fab IT setup:** MES, real-time tracking, 24/7 automation, robotics, and advanced analytics for yield optimisation.

- **Open-source PDKs:** Freely available design kits incl. SPICE models, standard cell libraries, and IP blocks for academic and industrial use.

- **Open software infrastructure:** Where possible based on European or open-source software (audits, adaptability, security).

- **Advanced packaging & chiplet-readiness:** From day 1, capacities for RDL/fan-out, interposer, co-packaging (**65 nm + logic**), UCIe support, and qualified **Known-Good-Die (KGD)** flows.

- **Certifiability & obsolescence management:** Technology pathways target long-availability processes with certifiability to industry standards (e.g., automotive, safety).

**Roadmap conclusion:** The technological roadmap provides a pragmatic, staged path: it enables a rapid start on proven technology, swift migration to the strategic **65-nm** node, and the systematic build-out of a Europe-wide fab network. This approach balances **time-to-market, risk minimisation, and replicability**—creating the foundation for **technological sovereignty, innovation, and economies of scale**. Europe can thus produce additional domestic chips in the short term and, in the medium term, establish a manufacturing ecosystem that sets global benchmarks for **security, openness, and resilience**.

## Workforce and training strategy

The **Transparent Reference Fab (TRF)** treats people as a strategic lever: **standardised role profiles** with clear levels (Engineer/Technician/Operator, **L1–L3**) and **RBAC** rights in the **MES** anchor **Comply-to-Connect** on the people side; **curricula, micro-credentials**, and a **skills passport** make qualification and re-certification measurable and auditable.

**Packaging-First** is established from day 1 as its own competence track (SiP/UCIe, RDL/fan-out, ATE/SLT). Development follows transparent paths (technical ladder and leadership) with mandatory leadership fundamentals and mentoring—so scaling does not depend on “hero managers” but on **standards, checks, and audits**. The strategy follows the staged technology roadmap **130 → 65 nm** and enables the fast, reproducible commissioning of identical fabs.

**Phase-0 note:** The following bandwidths and intake corridors are conservative guide values. Site-specific sizing (automation depth, product mix, shift model), MoUs with education/VET partners, RBAC/re-cert cycles, and the **family-ready** components (see below) are validated bottom-up in **Phase 0** and versioned as a binding part of the blueprint.

## Workforce pyramid and FTE corridors (base module ~5 k WSPM)

The organisation rests on eight job families: **process engineering, equipment/maintenance, production/operator, metrology/QA, facilities/EHS**,

**IT/MES/OT-security, packaging/test (ATE & SLT), and academy/training.** Demand is phase-dependent. In the ramp, engineering and maintenance roles dominate (tool IQ/OQ/PQ, ramp methodology); in 24/7 steady state, the operator share grows; during 65-nm qualification, load again rises in process and metrology. **Brownfield** lowers time-to-competence and initial FTE peaks (experienced crews, existing SOPs), while **greenfield** temporarily requires higher engineering and training capacity. Shift model and automation level (AMHS/robotics) are designed so that **TtC** is short, **OEE** stable, and **traceability/audit** always ensured.

### T1 – Workforce pyramid & FTE ranges (per phase; guide values)

| Job family                     | Ramp-up | SOP 130 nm | SOP 65 nm |

|--------------------------------|---------|------------|-----------|

| Process engineering            | 15–25   | 10–15      | 25–35     |

| Equipment/maintenance          | 25–40   | 15–25      | 25–35     |

| Production/operator            | 25–40   | 100–140    | 120–160   |

| Metrology/QA                   | 10–15   | 20–30      | 25–35     |

| Facilities/EHS                 | 10–15   | 15–20      | 15–20     |

| IT/MES/OT-security             | 8–12    | 10–15      | 12–20     |

| Packaging/test (ATE/SLT)       | 10–15   | 20–30      | 30–50     |

| Academy/training               | 6–10    | 6–10       | 6–10      |

| Cross-functional & management* | 25–40   | 60–90      | 80–120    |

\* Procurement/SCM, quality systems, HR/finance, HSE compliance, communications, site services (partly as shared services).

In full operation, headcount for the base module (incl. cross-functional) typically sits around **~350–500 FTE**. For the pipeline, plan **30–50 engineers** and **70–120 technicians/operators p.a.** during the build-up phase (2–3 years); in the steady phase, around **20** and **60 p.a.** respectively.

### RefFab Academy (training ecosystem)

The **RefFab Academy** acts as an umbrella with central curricula, trainer certification and a digital learning platform (**LXP**), plus regionally attachable hubs. Unified standards, **EQF-aligned micro-credentials** and a **skills passport** become part of **Comply-to-Connect** (personnel certification in parallel with process audit). Site-independent, replicable **Learning Cells** and a “**learning-workshop-in-a-box**” (outside sensitive cleanroom zones) ensure identical training environments. Partnerships with EU skills initiatives,

VET/chambers, universities, and OSAT/ATE OEMs ensure reach and interoperability; **ECTS/VET mapping** is maintained centrally.

Onboarding combines **6–12-week bootcamps** (cleanroom/EHS, tool basics, yield/metrology), **VR/AR-supported tool training** and **digital-twin simulators** with mentored on-the-job practice. Rotations between the Reference Fab, OSAT partners, and R&I shorten **time-to-competence (TtC)** and broaden practical experience. A **train-the-trainer** path professionalises scaling; **returnships** enable lateral and re-entry. All evidence feeds the **skills passport** and is **RBAC-linked** (re-cert typically **24–36 months**).

## T2 – Curriculum matrix & training times (extract)

| Module (example)                     | Target profiles           | Format/duration           | Completion/re-cert        |

|--------------------------------------|---------------------------|---------------------------|---------------------------|

| Cleanroom 101 / EHS/REACH/Seveso     | all                       | Bootcamp <b>1–2 weeks</b> | Badge L1 / <b>24 m</b>    |

| Litho/Etch/Dep basics                | Operator, Maint., Process | Bootcamp <b>2–3 weeks</b> | Badge L1 / <b>36 m</b>    |

| Yield/FA/Metrology                   | Process, QA               | Course <b>1–2 weeks</b>   | Micro-cred / <b>36 m</b>  |

| MES/Traceability/ISO 27001           | IT/MES, line leadership   | Course <b>1 week</b>      | Micro-cred / <b>24 m</b>  |

| AMHS maintenance L1 (with AR/VR)     | Maintenance               | Practice <b>1 week</b>    | Badge L1 / <b>24 m</b>    |

| UCle & chiplet test (ATE/SLT)        | Test/packaging            | Course <b>3–5 days</b>    | Badge / <b>24 m</b>       |

| Operator cross-training (litho/etch) | Operator                  | Rotation <b>4 weeks</b>   | Micro-cred / <b>24 m</b>  |

| Train-the-trainer                    | Senior specialists        | Course <b>1 week</b>      | Certificate / <b>36 m</b> |

The **skills passport** captures the sequence **recruiting** → **bootcamp** → **mentored on-the-job** → **L1** → **specialisation (packaging/test/IT/MES etc.)** → **L2/L3** with re-certifications. It also serves as evidence for the **Trusted-label audit**.

## Packaging-First tracks and test

In parallel with front-end, from day 1 build **RDL/fan-out, interposer/2.5D, flip-chip/microbump, UCle/die-to-die, SI/PI/thermal, KGD flows**, and **ATE/SLT**. The **minimum scope in years 1–2** includes an **RDL/flip-chip cell**, a **basic interposer flow**, an **ATE cell** (with DFT/DFM coupling) and **KGD screening**. This raises **system value per wafer**, ensures **chiplet-readiness**, and reduces dependencies on **OSAT** bottlenecks.

## Mobilisation, attraction & retention

Talent acquisition follows an active **sourcing and EVP** strategy: EU programmes (Chips Skills Academy, EIT), dual/integrated study models, **reskilling** from adjacent industries (pharma/optics/battery), **international recruitment** (Blue Card/relocation), and **referral programmes**. **Family-ready sites** increase retention and availability: **shift-compatible childcare** (allocated places with extended hours, back-up care, holiday/camp contingents, voucher/subsidy models, matching service), **language tracks**, and **mentoring** within a **Just-Culture**. Transparent career paths, **tech ladders**, certificate tiers, and a **network-wide badge economy** foster development and mobility; rotations are recognised as development steps. **KPIs** (e.g., time-to-offer, offer-acceptance rate, TtC@90/180 days, pipeline diversity, referral rate) steer effectiveness.

## Trusted personnel & compliance (people component of Comply-to-Connect)

The personnel part of the **Trusted label** covers **role-based rights** in the MES (least-privilege), **auditable training/re-cert evidence**, on-/off-boarding processes, and **risk-based, GDPR-compliant background checks** with clear purpose limitation, data minimisation, and short retention periods:

- **L0 – Standard:** identity check, diploma/reference check.

- **L1 – Cleanroom access:** + employment/gap check, passed safety induction.

- **L2 – Critical access** (e.g., MES admin/tool owner): + sanctions/embargo screening, extended references.

- **L3 – Highly critical (security/IP core):** + additional evidence only where legally permissible, **four-eyes** approval.

All checks are vendor-audited (processor agreements) and governed in works agreements/DPIA. The **audit trail** carries **aggregated people KPIs**, without personal details.

The **compliance gate** controls publication/artefacts via defined checks: **antitrust/competition, FDI/export/dual-use, IP/OSS compatibility**, and **privacy** (anonymisation/pseudonymisation where needed); each release receives a **release ID** and checklist evidence.

## KPI set and learning curves

For steering and scaling, use: **time-to-competence, quarterly OEE improvement, yield-ramp slope (130 → 65 nm), audit score (people part), attrition, time-to-hire/offer-acceptance rate, referral rate, academy throughput, and re-cert compliance**. Network-wide **MPWs/qualification runs** and **rotations** generate learning effects that measurably

shorten TtC and ramp time in clone fabs; **training pass rates and first-pass yield in learning cells** serve as leading indicators.

## Economic leverage and industrial-policy benefits

Beyond its technological and security objectives, the **Transparent Reference Fab (TRF)** has a clear economic-strategy dimension: with a manageable outlay of public funds, additional trustworthy manufacturing capacity on mature nodes is to be created—replicable to generate economies of scale and resilience for Europe—**complementary** to high-end initiatives, not in competition.

### **Cost efficiency through technology choice and brownfield levers:**

A 300-mm operation at 65/130 nm works **without EUV/High-NA**—the single biggest cost driver of modern <5-nm fabs falls away. Reference projects in Europe indicate **CAPEX in the low single-digit billions**; takeovers/refits of existing 300-mm fabs can further reduce time and investment needs. To secure clonability and auditability, “**certified tool families**” are defined (identical model series or quality-equivalent released variants). Refurbished tools are admissible only if they fall within these families and meet the specified process window in a like-for-like audit; otherwise, new equipment is required.

### **Faster payback via niches and a “trusted-premium” model:**

Target segments with higher willingness to pay (e.g., automotive safety/ASIL, aerospace/space-grade, **critical-infrastructure** electronics) carry the trusted model: auditable provenance, long-term availability (10–15+ years), documented quality KPIs, and prioritised delivery in crises justify price premia and stabilise cash flows. Public and semi-public demand anchors (authorities, rail/energy, defence, space) secure base load via multi-year offtake contracts (incl. take-or-pay), readiness/retainer payments, and—where sensible—**critical-infrastructure** sourcing quotas (“EU-Trustworthy”).

### **Co-operation—yes, voluntary and EU-law compliant:**

As an industrial-policy mechanism, the network targets **voluntary, compliant** economies of scale—underpinned by standards, audits, and fundable **pre-competitive** modules. Scale advantages arise voluntarily and in line with competition law: permitted are pre-competitive co-operations with **information hygiene** (e.g., open/standardised open PDKs, modular process/qualification data in aggregated/lagged form, joint MPW runs, framework procurements with firewalls, shared training curricula). **Not** shared: prices/margins, customer-specific capacities/volumes, future output or bidding strategies. **Chips Act/ECIC and IPCEI** mechanisms encourage such collaboration but do not dictate commercial policy. Governance rules ensure trustee/clean-room setups, data classification, opt-in modules, and auditability.

### **Specialisation of clone fabs: identical base, different niches:**

With a common 65-nm CMOS base, archetypes enable differentiation while preserving scale:

- **Automotive safety/ASIL** (AEC-Q100, ISO 26262; long-term availability) for safety-critical MCUs/ASICs,

- **RF/mixed-signal & sensing** (RF-SOI/eNVM) for IoT transceivers, radar front-ends, sensor ASICs,

- **Power & BCD (smart power)** for PMICs, gate drivers, and HV options (130 → 65 nm BCD),

- **Advanced-packaging hub** (RDL/fan-out, interposer/2.5D, co-packaging of 65-nm periphery with leading-edge logic, UCle interfaces),

- **Aerospace/space-grade** (ECSS/DO-254; radiation-tolerant/hard).

**Advanced packaging & chiplet-readiness** raise the **system value per wafer**, bridge procured leading-edge logic, and address Europe's gap in the **OSAT/interposer** segment—leveraging both margin and resilience. Politically, specialisation unlocks lead markets, boosts margin stability, and distributes value creation purposefully across regions and sectors.

#### **Ownership/operating models and cross-border scaling:**

Various models are possible, e.g. Various models are possible, e.g. PPP is one option alongside a public SPV, foundation/association, cooperative, or private ownership with or without a public-service mandate. Clone fabs can be operated by different EU states or public enterprises; prerequisites are uniform audit/security requirements, **open-access principles**, and compliance with state-aid/procurement rules. **Non-EU stakes** are considered only restrictively (FDI screening, minority limits, golden-share/trust conditions); core control remains in EU hands.

#### **Regional economic impulses and multiplier:**

A 5k WSPM unit creates several hundred **highly qualified** direct jobs; indirect/induced effects drive a substantial multiplier (suppliers, services, test/OSAT, training). The **distributed blueprint strategy**—combining strong clusters and structurally weaker regions—broadens participation and increases political feasibility. **Obsolescence services** (form-fit-function re-design, mask maintenance, long-term wafer saves) generate recurring revenue and bind customers over the product life cycle.

#### **Site costs realistic—and actively mitigated:**

Higher energy/water costs in Europe are addressed via **PPAs** and load management, water recycling/UPW recovery, modular automation (OPEX lever), predictive maintenance (MTBF↑, downtime↓), and a skills academy/dual programmes for talent security. This reduces time-to-yield and overall operating costs. Industrial policy flanks these measures with qualified state-aid frameworks, training programmes, and standardised energy instruments (e.g., PPAs).

#### **Complementarity with high-end initiatives:**

The TRF complements 2-nm pilot lines, **ESMC (28/22 nm)**, and other high-end projects: it

stabilises value creation, qualifies personnel/suppliers on mature nodes, provides complementary **advanced-packaging** services, and reduces dependencies in safety-critical supply chains.

#### **Measurability & governance as industrial-policy levers:**

Impact and trust are made transparent via **trust KPIs** (e.g., DPPM targets, audit score, level of transparency, lead-time reliability). The “**Trusted EU Fab Network**” label is tied to regular audits, data/IT-security requirements, **tool-family compliance**, and **defined transparency corridors**. **Comply-to-Connect** means: baseline standards (standards/PDKs, audit access, security) are mandatory; beyond that, operators may **opt into** co-operation modules (e.g., procurement, joint qualifications)—**without** exchanging commercially sensitive information.

#### **Conclusion:**

The TRF leverages mature nodes and a **no-EUV** approach to keep CAPEX low, monetises added value through **trusted-premium** positioning and **advanced packaging**, and scales via a **voluntary, law-compliant** network—**complementary** to Europe’s high-end path. An initial public seed investment can trigger a European “**silicon multiplier**”: new fabs, new business models (e.g., SME-focused foundry services), high-quality jobs, and additional strategic value creation. The crux is to couple technical scalability with smart demand anchors and a viable business/governance model—not as a technical parlour trick, but as the foundation of an industrial movement. The result is a **replicable, long-term competitive manufacturing ecosystem without permanent subsidies** that measurably strengthens Europe’s sovereignty, security, and resilience—and gradually reduces dependencies.

## Financing and preliminary timeline

Realising the **Transparent Reference Fab (TRF)** requires substantial financial resources—yet, as shown, orders of magnitude below leading-edge fab projects. For a **300-mm base module (~5,000 wafer starts/month) on 130 → 65 nm without EUV**, a robust corridor can be derived from European comparison projects and market benchmarks. **Important:** the figures given here are indicative; a precise bottom-up calculation will be carried out as part of the feasibility study (Phase 0).

### Investment costs (CAPEX)

Investment for a 300-mm facility at 130/65 nm depends strongly on the approach (greenfield vs brownfield), the day-1 packaging scope, and the tool policy (defined **tool families**, quality-equivalent vs refurbished). Current experience suggests the following orders of magnitude:

- **New build (greenfield):** A completely new plant with up-to-date 300-mm infrastructure (buildings, cleanrooms, utilities), a digital backbone

(MES/traceability/SecOps), and new DUV-capable process tools typically lies in the **1–2 bn € corridor** for a base module (~5k WSPM). Reference anchors: **Bosch Dresden (~1 bn €, start-up 2021)** and **Infineon Villach (~1.6 bn €, 2021)**. [Bosch, 2021; Infineon, 2021]. For higher initial capacities (>10k WSPM) costs rise accordingly. At <7-nm level (EUV), comparable projects are **orders of magnitude higher (>10 bn €)**.

- **Conversion/expansion (brownfield):** Where existing 300-mm infrastructure (buildings, cleanrooms, utilities) can be used or expanded, time and capital needs fall significantly. Depending on asset quality and target node, a solution **well below 1 bn €** is possible. A prominent anchor is **onsemi's acquisition of GF East Fishkill (300 mm, 65/45 nm) for ~430 M \$** (plus refit/invest), demonstrating that legacy infrastructure can cut capital needs by a factor of **2–3**.

- **Use of refurbished equipment:** As **~70–80%** of fab investment is process equipment, selective use of refurbished 300-mm tools can bring substantial savings (**typically 30–70%** vs new, depending on generation/availability). For clonability and auditability, however, only **defined tool families** (identical or quality-certified model series) are admissible, with verification of the specified process window in an equivalent audit; otherwise, new equipment.

- **Packaging-First (as a CAPEX block):** An integrated back-end module (RDL/fan-out, interposer/2.5D, flip-chip/microbump, ATE/SLT) is co-planned from day 1 and scaled in phases. Depending on scope, **packaging-readiness adds ~+10–20%** to front-end CAPEX. Benefits: shorter time-to-market for SiP/chiplet solutions, higher value per wafer, resilience against OSAT bottlenecks. European anchors (e.g., advanced-packaging investments in IT) underline the strategic relevance.

**Note on scaling:** The target capacity of **~60,000 wafers/year (base module)** is deliberately small—modern “gigafabs” achieve multiples thereof. Studies cite an efficient minimum scale for 300-mm logic around **~40k WSPM**; the Reference Fab is therefore **modular by design** (cleanroom, utilities, logistics) and can grow linearly towards **10k+ WSPM** via additional tool clusters/shift models.

**“As large as necessary, as modular as possible”**—scalability is engineered in without over-investing upfront.

## Operating costs (OPEX)

Annual operating costs for a 300-mm facility of this size, at full load, fall in the **high eight-digit to low nine-digit € range**. Key OPEX factors are:

- **Personnel:** For ~5k WSPM—depending on automation and shift model—**several hundred** specialists are required (process/equipment engineers, technicians, operators, quality, logistics, IT). Reference anchor: **Bosch Dresden** reports **~700 employees** at full build-out (with a different product/capacity structure). For the Reference Fab, an initial corridor of **~400–600 FTE** can be assumed.

- **Energy & utilities:** Continuous load in the **double-digit MW** range for HVAC, cooling, vacuum/exhaust treatment, UPW generation, etc. At EU industrial power prices (with PPAs/load management) this results in **tens of millions € p.a.**; added to this are water/wastewater, gases/chemicals (with recovery/abatement). **UPW recycling (30–50%)** and heat-recovery lower medium-term costs.

- **Materials & maintenance:** Bare wafers, resists/developers, process gases (Ar, H<sub>2</sub>, N<sub>2</sub>, F-gases), etch chemicals, spare parts/service contracts. **Preventive maintenance** and in-house spare pools stabilise MTBF and reduce downtime; as a rule of thumb, **5–10% of tool depreciation p.a.** is a maintenance corridor.

- **Other fixed costs:** Facility management (cleanroom classes), IT/MES/cybersecurity, insurance, waste disposal, licences (where needed).

#### OPEX orientation (corridors, at ~60k wafers/year):

| Cost category           | Order of magnitude p.a. | Notes                                                        |

|-------------------------|-------------------------|--------------------------------------------------------------|

| Personnel               | <b>50–80 M €</b>        | ~400–600 FTE incl. shift operation [Bosch, 2021]             |

| Energy & utilities      | <b>15–30 M €</b>        | Power/UPW/gases/chemicals (EU price band, efficiency levers) |

| Materials & maintenance | <b>30–50 M €</b>        | Wafers, chemicals, spare parts, service contracts            |

| Other fixed costs       | <b>10 M €+</b>          | Facilities, IT/MES, insurance, waste                         |

| <b>Total OPEX</b>       | <b>~100–150 M €</b>     | At full utilisation; higher in ramp years (yield effects)    |

**Context:** Wafer prices and manufacturing costs are **significantly lower on mature nodes** than at the leading edge; this improves economics at medium volumes but requires high utilisation and **stable demand anchors**.

#### Validation via comparison projects

Multiple projects in Europe and internationally confirm the above metrics and provide experiential data:

- **Bosch Dresden (DE)** – 300 mm, 65 nm and above: opened 2021 as a “wafer fab of the future”. **~1 bn €** investment, build time ~3 years (2018–2021), **~700 employees** at full build-out. High automation accelerated the ramp (start ~6 months earlier than planned). **Relevance:** cost framework and timeline for a European 300-mm facility in the mature segment.

- **STMicroelectronics/GlobalFoundries Crolles (FR)** – 300 mm, FD-SOI ~18 nm: announced 2022; target capacity up to **620k wafers/year (~51.6k/month)** at full

build-out. **~7.5 bn €** investment (incl. infrastructure/ramp), **~2.9 bn €** public funding; project **temporarily slowed/paused in 2025** (demand uncertainty). **Relevance:** scale effects & state-aid logic for large mature-node projects; market risk at very high volumes.

- **ESMC – TSMC/Bosch/Infineon/NXP (DE)** – 300 mm, 28–12 nm: started 2024; planned output **~40k WSPM**, investment **>10 bn €**, aid **~5 bn €**. SOP targeted end-2027, full capacity around 2029. **Relevance:** leading-edge scale (significantly more expensive) but illustrates EU aid/timeline logic.

- **Infineon “Smart Power Fab” Dresden (DE)** – 300 mm power: ground-breaking 2023, **~5 bn €** investment, **~1 bn €** funding; start-up from 2026, full build-out 2030+. **Relevance:** more-than-Moore scale and phased expansion.

## Financing and institutional anchoring

Realising the **European Reference Fab** requires significant funds yet remains strategically favourable relative to modern leading-edge plants. The following statements are indicative; Phase 0 will validate and specify them.

- **Investment frame & strategy:** The fab is conceived as **European public-interest infrastructure**—with **open PDK**, audit transparency, and **Packaging-First** as **first-of-a-kind** features (eligible for state aid). **Tranche-based financing** ties disbursements to milestones (construction progress, tool IQ/OQ, PDK/MPW start, audit go-live, 65-nm release).

- **Preferred model: PPP (public–private).**

- **Public sector** (EU, national, possibly regional) covers planning, construction/facility, training, and initial process/PDK development.

- **Private partners** (industry, suppliers, user sectors) co-invest in equipment, working capital, and co-developments.A possible target model is a **European Reference Fab Foundation**, curating operations, standardisation (tool-family policy/PDK), Comply-to-Connect, and the openness of the blueprint (**public-trust mandate**).

### Funding sources:

1. **EU programmes:** Chips Act/FOAK, Horizon Europe, EIC, IPCEI Microelectronics/Communication.

2. **National funds:** host-country support (construction, energy infrastructure, training).

3. **Industry consortia:** equity shares/special-purpose vehicles (e.g., automotive, defence, telecom, IoT) in return for quotas/board seats—**without** constraining open access.

4. **European partner states:** co-investments by associated countries (CH/NO/UK) in return for know-how access.

5. **Innovative instruments:** project bonds, green-tech infrastructure funds, public-trust endowments (ESA-analogous) to secure operations.

**Long-term financing and scaling:** After successful establishment of the first Reference Fab, public support recedes stepwise. **Follower fabs** become increasingly privately/regionally financed; the central entity provides governance, auditing, training, and PDK/MPW maintenance. The result is a scalable, **European-controlled network** that can raise Europe's current ~9% share of global chip production over time.

### Transparency and replication